ການອອກແບບຂອງໂຟໂຕນິກວົງຈອນປະສົມປະສານ

ວົງຈອນປະສົມປະສານໂຟໂຕນິກ(PIC) ມັກຖືກອອກແບບດ້ວຍຄວາມຊ່ວຍເຫຼືອຂອງສະຄຣິບທາງຄະນິດສາດເນື່ອງຈາກຄວາມສຳຄັນຂອງຄວາມຍາວຂອງເສັ້ນທາງໃນອິນເຕີເຟໂຣມິເຕີ ຫຼື ແອັບພລິເຄຊັນອື່ນໆທີ່ມີຄວາມອ່ອນໄຫວຕໍ່ຄວາມຍາວຂອງເສັ້ນທາງ.PICຖືກຜະລິດໂດຍການສຸ່ມຫຼາຍຊັ້ນ (ໂດຍປົກກະຕິແມ່ນ 10 ຫາ 30) ໃສ່ແຜ່ນເວເຟີ, ເຊິ່ງປະກອບດ້ວຍຮູບຊົງຫຼາຍຫຼ່ຽມຫຼາຍຮູບ, ມັກຈະສະແດງຢູ່ໃນຮູບແບບ GDSII. ກ່ອນທີ່ຈະສົ່ງໄຟລ໌ໄປຫາຜູ້ຜະລິດໂຟໂຕມາສ, ມັນເປັນສິ່ງທີ່ຕ້ອງການຢ່າງຍິ່ງທີ່ຈະສາມາດຈຳລອງ PIC ເພື່ອກວດສອບຄວາມຖືກຕ້ອງຂອງການອອກແບບ. ການຈຳລອງແບ່ງອອກເປັນຫຼາຍລະດັບ: ລະດັບຕໍ່າສຸດແມ່ນການຈຳລອງແມ່ເຫຼັກໄຟຟ້າສາມມິຕິ (EM), ບ່ອນທີ່ການຈຳລອງຖືກປະຕິບັດຢູ່ໃນລະດັບຄວາມຍາວຄື່ນຍ່ອຍ, ເຖິງແມ່ນວ່າການພົວພັນລະຫວ່າງອະຕອມໃນວັດສະດຸແມ່ນຖືກຈັດການໃນລະດັບມະຫາພາກ. ວິທີການທົ່ວໄປປະກອບມີໂດເມນເວລາຄວາມແຕກຕ່າງຈຳກັດສາມມິຕິ (3D FDTD) ແລະການຂະຫຍາຍ eigenmode (EME). ວິທີການເຫຼົ່ານີ້ແມ່ນຖືກຕ້ອງທີ່ສຸດ, ແຕ່ບໍ່ສາມາດປະຕິບັດໄດ້ສຳລັບເວລາການຈຳລອງ PIC ທັງໝົດ. ລະດັບຕໍ່ໄປແມ່ນການຈຳລອງ EM 2.5 ມິຕິ, ເຊັ່ນ: ການຂະຫຍາຍລຳແສງຄວາມແຕກຕ່າງຈຳກັດ (FD-BPM). ວິທີການເຫຼົ່ານີ້ໄວກວ່າຫຼາຍ, ແຕ່ເສຍສະລະຄວາມຖືກຕ້ອງບາງຢ່າງ ແລະ ສາມາດຈັດການການຂະຫຍາຍພັນ paraxial ເທົ່ານັ້ນ ແລະ ບໍ່ສາມາດໃຊ້ເພື່ອຈຳລອງເຄື່ອງສະທ້ອນແສງໄດ້, ຕົວຢ່າງ. ລະດັບຕໍ່ໄປແມ່ນການຈຳລອງ EM 2D, ເຊັ່ນ 2D FDTD ແລະ 2D BPM. ສິ່ງເຫຼົ່ານີ້ຍັງໄວກວ່າ, ແຕ່ມີໜ້າທີ່ຈຳກັດ, ເຊັ່ນວ່າພວກມັນບໍ່ສາມາດຈຳລອງຕົວໝູນໂພລາໄຣເຊຊັນໄດ້. ລະດັບຕໍ່ໄປແມ່ນການຈຳລອງແມັດຕຣິກສົ່ງຕໍ່ ແລະ/ຫຼື ການກະແຈກກະຈາຍ. ແຕ່ລະອົງປະກອບຫຼັກຖືກຫຼຸດລົງເປັນອົງປະກອບທີ່ມີອິນພຸດ ແລະ ຜົນຜະລິດ, ແລະ ຄື້ນນຳທາງທີ່ເຊື່ອມຕໍ່ຖືກຫຼຸດລົງເປັນອົງປະກອບການປ່ຽນໄລຍະ ແລະ ການຫຼຸດຜົນກະທົບ. ການຈຳລອງເຫຼົ່ານີ້ແມ່ນໄວຫຼາຍ. ສັນຍານຜົນຜະລິດແມ່ນໄດ້ຮັບໂດຍການຄູນແມັດຕຣິກສົ່ງຕໍ່ດ້ວຍສັນຍານອິນພຸດ. ແມັດຕຣິກກະຈາຍ (ເຊິ່ງອົງປະກອບເອີ້ນວ່າພາລາມິເຕີ S) ຄູນສັນຍານອິນພຸດ ແລະ ຜົນຜະລິດຢູ່ດ້ານໜຶ່ງເພື່ອຊອກຫາສັນຍານອິນພຸດ ແລະ ຜົນຜະລິດຢູ່ອີກດ້ານໜຶ່ງຂອງອົງປະກອບ. ໂດຍພື້ນຖານແລ້ວ, ແມັດຕຣິກກະຈາຍມີການສະທ້ອນພາຍໃນອົງປະກອບ. ແມັດຕຣິກກະຈາຍມັກຈະມີຂະໜາດໃຫຍ່ເປັນສອງເທົ່າຂອງແມັດຕຣິກສົ່ງຕໍ່ໃນແຕ່ລະມິຕິ. ໂດຍສະຫຼຸບແລ້ວ, ຈາກ EM 3D ຈົນເຖິງການຈຳລອງແມັດຕຣິກສົ່ງຕໍ່/ການກະແຈກກະຈາຍ, ແຕ່ລະຊັ້ນຂອງການຈຳລອງນຳສະເໜີການແລກປ່ຽນລະຫວ່າງຄວາມໄວ ແລະ ຄວາມແມ່ນຍຳ, ແລະ ຜູ້ອອກແບບເລືອກລະດັບການຈຳລອງທີ່ເໝາະສົມສຳລັບຄວາມຕ້ອງການສະເພາະຂອງພວກເຂົາເພື່ອເພີ່ມປະສິດທິພາບຂະບວນການກວດສອບການອອກແບບ.

ເຖິງຢ່າງໃດກໍ່ຕາມ, ການອີງໃສ່ການຈຳລອງແມ່ເຫຼັກໄຟຟ້າຂອງອົງປະກອບສະເພາະ ແລະ ການໃຊ້ແມັດຕຣິກການກະແຈກກະຈາຍ/ການໂອນຍ້າຍເພື່ອຈຳລອງ PIC ທັງໝົດບໍ່ໄດ້ຮັບປະກັນການອອກແບບທີ່ຖືກຕ້ອງຢ່າງສົມບູນຢູ່ຕໍ່ໜ້າແຜ່ນໄຫຼ. ຕົວຢ່າງ, ຄວາມຍາວຂອງເສັ້ນທາງທີ່ຄິດໄລ່ຜິດພາດ, ຄື້ນນຳທາງຫຼາຍໂໝດທີ່ບໍ່ສາມາດສະກັດກັ້ນຮູບແບບລຳດັບສູງໄດ້ຢ່າງມີປະສິດທິພາບ, ຫຼື ຄື້ນນຳທາງສອງອັນທີ່ຢູ່ໃກ້ກັນເກີນໄປ ເຊິ່ງນຳໄປສູ່ບັນຫາການເຊື່ອມຕໍ່ທີ່ບໍ່ຄາດຄິດ ມັກຈະບໍ່ໄດ້ຮັບການກວດພົບໃນລະຫວ່າງການຈຳລອງ. ດັ່ງນັ້ນ, ເຖິງແມ່ນວ່າເຄື່ອງມືການຈຳລອງຂັ້ນສູງໃຫ້ຄວາມສາມາດໃນການກວດສອບການອອກແບບທີ່ມີປະສິດທິພາບ, ແຕ່ມັນຍັງຕ້ອງການຄວາມລະມັດລະວັງໃນລະດັບສູງ ແລະ ການກວດກາຢ່າງລະມັດລະວັງໂດຍຜູ້ອອກແບບ, ບວກກັບປະສົບການຕົວຈິງ ແລະ ຄວາມຮູ້ດ້ານວິຊາການ, ເພື່ອຮັບປະກັນຄວາມຖືກຕ້ອງ ແລະ ຄວາມໜ້າເຊື່ອຖືຂອງການອອກແບບ ແລະ ຫຼຸດຜ່ອນຄວາມສ່ຽງຂອງແຜ່ນໄຫຼ.

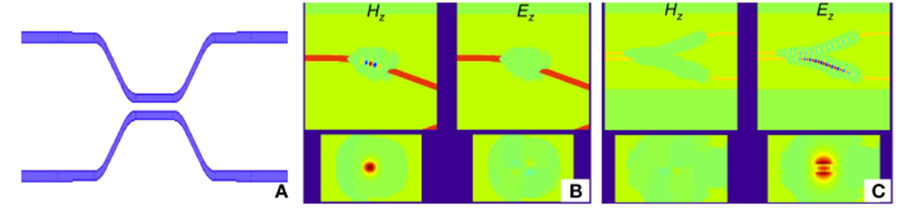

ເຕັກນິກທີ່ເອີ້ນວ່າ sparse FDTD ຊ່ວຍໃຫ້ການຈຳລອງ FDTD ແບບ 3D ແລະ 2D ສາມາດປະຕິບັດໄດ້ໂດຍກົງໃນການອອກແບບ PIC ທີ່ສົມບູນເພື່ອກວດສອບການອອກແບບ. ເຖິງແມ່ນວ່າມັນຍາກສຳລັບເຄື່ອງມືການຈຳລອງແມ່ເຫຼັກໄຟຟ້າໃດໆທີ່ຈະຈຳລອງ PIC ຂະໜາດໃຫຍ່ຫຼາຍ, FDTD ແບບ sparse ສາມາດຈຳລອງພື້ນທີ່ທ້ອງຖິ່ນທີ່ຂ້ອນຂ້າງໃຫຍ່. ໃນ FDTD 3D ແບບດັ້ງເດີມ, ການຈຳລອງເລີ່ມຕົ້ນດ້ວຍການເລີ່ມຕົ້ນອົງປະກອບຫົກຢ່າງຂອງສະໜາມແມ່ເຫຼັກໄຟຟ້າພາຍໃນປະລິມານທີ່ຖືກຄິດໄລ່ສະເພາະ. ເມື່ອເວລາຜ່ານໄປ, ອົງປະກອບສະໜາມໃໝ່ໃນປະລິມານຈະຖືກຄິດໄລ່, ແລະອື່ນໆ. ແຕ່ລະຂັ້ນຕອນຕ້ອງການການຄິດໄລ່ຫຼາຍ, ສະນັ້ນມັນໃຊ້ເວລາດົນ. ໃນ FDTD 3D ແບບ sparse, ແທນທີ່ຈະຄິດໄລ່ໃນແຕ່ລະຂັ້ນຕອນຢູ່ແຕ່ລະຈຸດຂອງປະລິມານ, ລາຍຊື່ຂອງອົງປະກອບສະໜາມຈະຖືກຮັກສາໄວ້ເຊິ່ງສາມາດສອດຄ່ອງກັບປະລິມານຂະໜາດໃຫຍ່ຕາມໃຈມັກ ແລະ ຖືກຄິດໄລ່ສະເພາະສຳລັບອົງປະກອບເຫຼົ່ານັ້ນເທົ່ານັ້ນ. ໃນແຕ່ລະຂັ້ນຕອນເວລາ, ຈຸດທີ່ຢູ່ຕິດກັບອົງປະກອບສະໜາມຈະຖືກເພີ່ມ, ໃນຂະນະທີ່ອົງປະກອບສະໜາມທີ່ຕໍ່າກວ່າຂອບເຂດພະລັງງານທີ່ແນ່ນອນຈະຖືກຫຼຸດລົງ. ສຳລັບໂຄງສ້າງບາງຢ່າງ, ການຄິດໄລ່ນີ້ສາມາດໄວກວ່າ FDTD 3D ແບບດັ້ງເດີມຫຼາຍລຳດັບ. ເຖິງຢ່າງໃດກໍ່ຕາມ, FDTDS ທີ່ຫາຍາກບໍ່ໄດ້ຜົນດີເມື່ອຈັດການກັບໂຄງສ້າງການກະຈາຍຕົວ ເພາະວ່າພາກສະໜາມເວລານີ້ກະຈາຍຫຼາຍເກີນໄປ, ເຊິ່ງສົ່ງຜົນໃຫ້ລາຍຊື່ຍາວເກີນໄປ ແລະ ຍາກທີ່ຈະຈັດການ. ຮູບທີ 1 ສະແດງຕົວຢ່າງພາບໜ້າຈໍຂອງການຈຳລອງ FDTD 3D ທີ່ຄ້າຍຄືກັບເຄື່ອງແຍກລຳແສງໂພລາໄຣເຊຊັນ (PBS).

ຮູບທີ 1: ຜົນໄດ້ຮັບການຈຳລອງຈາກ FDTD ແບບກະຈັດກະຈາຍ 3D. (A) ແມ່ນມຸມມອງດ້ານເທິງຂອງໂຄງສ້າງທີ່ຖືກຈຳລອງ, ເຊິ່ງເປັນຕົວເຊື່ອມຕໍ່ທິດທາງ. (B) ສະແດງພາບໜ້າຈໍຂອງການຈຳລອງໂດຍໃຊ້ການກະຕຸ້ນ quasi-TE. ແຜນວາດສອງອັນຂ້າງເທິງສະແດງໃຫ້ເຫັນມຸມມອງດ້ານເທິງຂອງສັນຍານ quasi-TE ແລະ quasi-TM, ແລະແຜນວາດສອງອັນຂ້າງລຸ່ມນີ້ສະແດງໃຫ້ເຫັນມຸມມອງຕັດຂວາງທີ່ສອດຄ້ອງກັນ. (C) ສະແດງພາບໜ້າຈໍຂອງການຈຳລອງໂດຍໃຊ້ການກະຕຸ້ນ quasi-TM.

ເວລາໂພສ: ກໍລະກົດ-23-2024